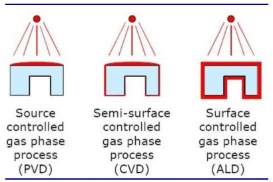

薄膜沉积是集成电路制造过程中必不可少的环节,传统的薄膜沉积工艺主要有 PVD、 CVD 等气相沉积工艺:

PVD(物理气相沉积): 在真空条件下,采用物理方法,将材料源(固体或液体) 表面 气化成气态原子、分子或部分电离成离子,并通过低压气体(或等离子体)过程,在基体表面沉积具有某种特殊功能的薄膜的技术。 PVD 主要方法包括真空蒸度、溅射镀膜等, 不仅可沉积金属膜、合金膜, 还可以沉积化合物、陶瓷、半导体、聚合物膜等,所涉及材料包括所有固体(C、 Ta、 W 困难)、卤化物和热稳定化合物。

CVD(化学气相沉积): 主要是利用含有薄膜元素的一种或几种气相化合物或单质、在衬底表面上进行化学反应生成薄膜的方法。 CVD 法可制作薄膜材料包括碱及碱土类以外的金属(Ag、 Au 困难)、碳化物、氮化物、硼化物、氧化物、硫化物、硒化物、碲化物、金属 化合物、合金等。

随着集成电路集成度越来越高,尺寸越来越小,高介电常数(high k)栅介质逐渐替代传统的氧化硅栅,同时高宽比越来越大,对沉积技术的台阶覆盖能力提出了更高的要求,因此 ALD 作为能够满足以上要求的新型沉积工艺已被越来越多的采用:

ALD(原子层沉积) : 可以理解为一种变相的 CVD 工艺,通过将气相前驱体脉冲交替地 通入反应器并在沉积基体上化学吸附并反应形成沉积膜的一种方法。与传统 CVD 不同的是,ALD 在沉积过程中, 反应前驱体是交替沉积, 新一层原子膜的化学反应是直接与之前一层相关联的,这种方式使每次反应只沉积一层原子。 ALD 已沉积材料包括金属、氧化物、碳(氮、硫、硅)化物、各类半导体材料和超导材料等。

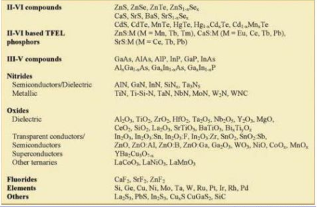

ALD沉积材料

ALD 相比传统的 PVD 和 CVD 等淀积工艺, 充分利用表面饱和反应,天生具备厚度控制和 高度的稳定性能,对温度和反应物通量的变化不太敏感。 因此 ALD 法沉积的薄膜兼具高纯度和高密度,既平整又具有高度的保型性,即使对于纵宽比高达 100:1 的结构也可实现良好的阶梯覆盖。 而 ALD 此前主要缺点在于沉积速度较慢,大约 1 Å/min,但是随着目前沉积薄膜层厚度要求越来越薄,这一缺点的影响已不再成为问题。 ALD 开始在栅氧化层,扩散阻挡层和存储器结构中的电极薄膜层应用越来越广泛。

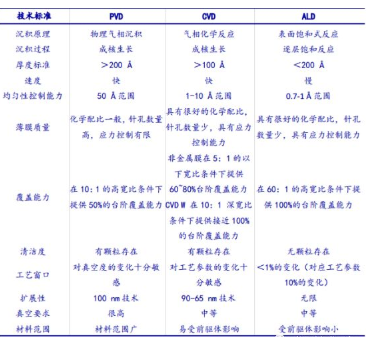

PVD、 CVD、 ALD 工艺特性比较

对于 ALD 工艺,前驱体的选择通常需要满足以下要求:(1) 在沉积温度下具有足够的 蒸汽压,以保证其能充分覆盖基底材料表面;(2)良好的热稳定性和化学稳定性,在沉积温度下不会发生自分解;(3)高反应性,保证其在基底表面迅速发生化学吸附,或与材料表面基团快速发生有效的反应,从而使表面膜具有高纯度;(4)反应副产物对基底和表面膜没有腐蚀性;(5)材料来源广泛, 低毒性。

常用的 ALD 前驱体包括非金属前驱体和金属前驱体。 非金属前驱体如卤化物(SiCl4、AlCl3等)、氮化物(NH3、(CH3)NNH2、BuNH2等),金属前驱体如烷基前驱体(Ga(CH3)3、Mg(C2H5)2)、 β-二酮前驱体(La(thd)3、Ca(thd)2)、醇盐前驱体(Ta(OC2H5)5、 Zr[(OC)(CH3)3]4)、烷基胺及硅胺基前驱体(Ti[N(C2H5CH3)2]4、 Pr[N(SiMe3)2]3) 等等。

3D NAND 的制造工艺十分复杂,主要包括高深宽比的沟开挖(High aspect ratio trenches)、在源与漏中不掺杂(No doping on source ordrain)、完全平行的侧壁(Perfectly parallel walls)、众多级的台阶(Tens of stairsteps)、在整个硅片面上均匀的淀积层(Uniform layer across wafer)、一步光刻楼梯成形(Single-Lithostairstep)、硬掩模刻蚀(Hard mask etching)、通孔工艺(Processing inside of hole)、孔内壁淀积工艺(Deposition on hole sides)、多晶硅沟道(Polysilicon channels)、电荷俘获型存储(Charge trap storage)、多种材料的通孔刻蚀(Etch through varying materials)、复合多层膜沉积(Deposition of tens of layers)等。

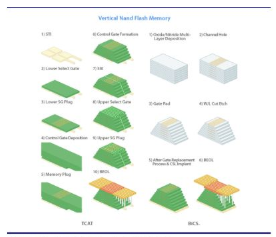

3D NAND 基本工艺流程

由于 3D NAND 复杂结构需要制造高的纵深比,相关流程包括叠层沉积、高深宽比通道孔蚀刻、字线金属化、阶梯蚀刻、高深宽比狭缝蚀刻,以及阶梯接触线成型等。 其中叠层沉积和自线金属化对沉积工艺提出了极高要求,在这方面 ALD 工艺比传统 CVD 及 PVD 工艺更具优势。

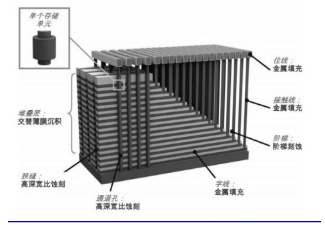

3D NAND 结构及关键沉积、蚀刻流程

ALD 工艺可有效减小应力。 3D NAND 堆叠存储单元的制造环节起始于交替薄膜沉积, 精 确控制每层薄膜厚度的均一性至关重要, 晶圆翘曲和局部薄膜应力直接影响到光刻叠对精度, 薄膜的厚度和重复性则影响存储单元的有效体积和光刻/蚀刻表现的一致性。因此,薄膜应力控制和良好的均匀性对晶圆良率十分关键。 同时,在采用置换栅极工艺的 3D NAND中,同层中存储单元的导线连接靠钨填充实现, 传统化学 CVD 钨薄膜具有高伸张应力,会导致晶圆翘曲,同时工艺带来的氟元素会扩散到邻层,造成缺陷并影响良率。 而采用低氟钨(LFW) 的 ALD 工艺可以制造出更光滑的表面形貌,更紧密地贴合每个填充层,从而减小沉积流程产生的应力。 相比于传统 CVD 钨沉积技术, ALD 低氟钨技术可降低一个数量级以上的应力(GPa→hMPa)、 99%的氟含量以及 30%以上的电阻率。

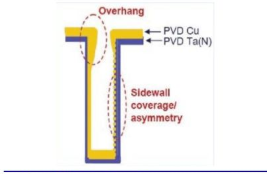

ALD 沉积薄膜均匀性更高,产生的应力最小

除了有效控制应力, ALD 具有更好的台阶覆盖能力,可满足 3D NAND 制造过程中高深 宽比的要求。 随着 3D NAND 层数的增加,孔道的深宽比也不断加大,制造中需要在深宽比100: 1 的孔道中纵向和横向高 K 介质(Al2O3)、钛阻挡层(Ti/TiN)等物质。 由于 ALD 沉积过程可有效控制薄膜的厚度和均匀性,因此可以实现高深宽比孔道的均匀覆盖,而 PVD 和CVD 对于高深宽比的台阶则无法实现均匀覆盖,约接近台阶顶部厚度越厚,若台阶的深宽比过高,可能会造成顶部开口堵塞。

PVD 等方法通常无法实现高深宽比的均匀覆盖

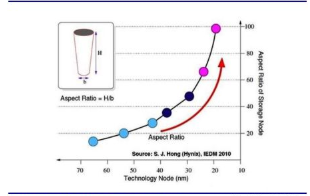

不仅 3D NAND 如此, 平面 DRAM 最重要也最艰难的挑战,是储存电容的高深宽比。 储存电容的深宽比会随着元件制程微缩而呈倍数增加,导致平面 DRAM 的制程微缩会越来越困难,因此 ALD 工艺在平面 DRAM 及 NAND 中也有重要应用。

DRAM 制程越窄,深宽比越高